# Garrett's Workshop GW419X-series 30-pin RAM SIMM Product Selection Guide

# Overview

The GW419X-series RAM SIMMs are 30-pin DRAM SIMMs. Capacities from 4 MB to 16 MB are available along with special-purpose variants.

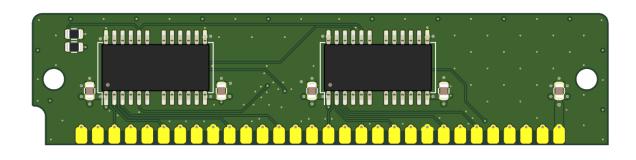

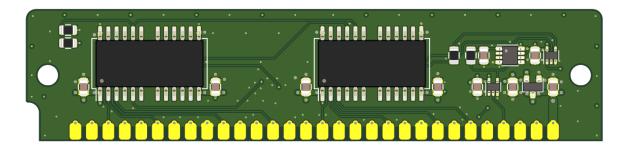

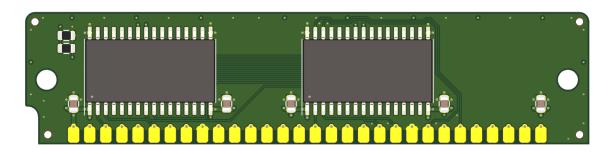

## High-Quality PCB

GW419X-series RAM SIMMs are built with an ENIG gold-plated, 4-layer PCB, and only new parts are used to build the SIMMs. All units are tested extensively before shipment.

## **Excellent Signal Integrity**

GW419X-series RAM SIMMs feature solid power and ground planes. Particular attention is paid to signal integrity, ensuring reliable performance on the fastest machines. Data and address buses are routed on separate layers as much as possible to minimize crosstalk. All bottom-side traces are run as asymmetric striplines shielded inside the SIMM PCB, reducing interference generated by large SIMM arrays. Particular attention was paid to the edge-sensitive RAS and CAS signals. These were optimized for minimum length, with ample spacing provided between these edge-sensitive signals and all other signals and buses. All GW419X-series SIMMs are non-composite 2- or 3-chip designs, reducing address bus loading compared to 8- and 9-chip SIMMs.

#### Open-Source Design

The GW419X-series RAM SIMM designs are fully open-source. The schematics and board layouts are all freely available for commercial and noncommercial use. To download the design files, visit the Garrett's Workshop GitHub page: <a href="https://github.com/garrettsworkshop">https://github.com/garrettsworkshop</a>

# **Product Selection Table**

| Model   | Capacity | Speed  | Description                                                                                                       |

|---------|----------|--------|-------------------------------------------------------------------------------------------------------------------|

| GW4190A | 4M x 8   | ≤ 70ns | 4 MB, 2K-refresh, 30-pin FPM DRAM SIMM, non-parity                                                                |

| GW4191A | 4M x 9   | ≤ 70ns | 4 MB, 2K-refresh, 30-pin FPM DRAM SIMM, with parity                                                               |

| GW4192A | 16M x 8  | ≤ 70ns | 16 MB, 4K-refresh, 30-pin FPM DRAM SIMM, non-parity                                                               |

| GW4194A | 4M x 8   | ≤ 80ns | 4 MB, 2K-refresh, 30-pin FPM DRAM SIMM for systems not supporting the 4M CBR protocol (e.g. Macintosh II and IIx) |

# Physical Dimensions (applicable to all GW419X-series RAM SIMMs)

| Parameter | Value                |

|-----------|----------------------|

| Height    | 20.574 mm ± 0.454 mm |

| Width     | 88.9 mm ± 0.2 mm     |

| Thickness | < 8 mm               |

| Weight    | < 28 g               |

#### Note Regarding FPM and EDO Bus Protocols

GW419X RAM SIMMs exclusively support the FPM ("fast page mode") bus protocol. GW419X-series SIMMs do not support the EDO ("extended data out", also known as "hyper page mode") bus protocol. However, GW419X DRAM SIMMs sometimes are built with EDO RAM ICs. When EDO ICs are used, the OE line of the DRAM ICs are tied to the CAS signal, disabling the extended data out feature and making the SIMM fully FPM-compatible. Because the GW419X-series SIMMs are all 2- and 3-IC designs, SIMMs built with EDO ICs still feature a lower-than-standard CAS signal loading of 4 or 5 IC-equivalents.