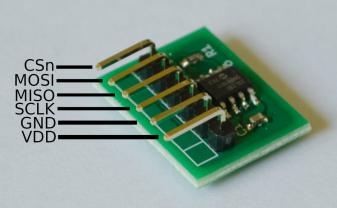

## SPI RAM 4Mb Datasheet (Rev. 1)

The SPI RAM 4Mb module is a RAM expansion module with a 1x6 PMOD style 0.1" male pin header. The module contains a single IS62WVS5128FBLL-20 SRAM chip. The chip is arranged as two stacked 2Mbit dies.

On board components provide power supply capacitor and pullup resistor on chip select.

Complete details for the memory chip and its features can be obtained from the manufacturer's datasheet:

http://www.issi.com/WW/pdf/IS62-65WVS5128FALL-BLL.pdf

## **Features Overview**

- Total Memory: 4 Mbit organized as 512K x 8-bit

- Max SCLK Frequency: 20 MHz

- 6-pin PMOD compatible pinout

- CS pullup 10K resistor

- 100n power decoupling capacitor

- byte or page operation. See manufacturer datasheet.

| Pin Number | Name | Function                    |  |

|------------|------|-----------------------------|--|

| 1          | CS   | Active-low chip select      |  |

| 2          | MOSI | Master output, Slave input. |  |

| 3          | MISO | Master input, Slave output  |  |

| 4          | SCLK | Serial clock input pin.     |  |

| 5          | GND  | Ground                      |  |

| 6          | VDD  | Power, 2.5V to 3.3V.        |  |

## Pinout

## IMPORTANT!!!

\*\*\*If combining multiple devices on a single SPI bus, to avoid bus contention ensure only one device's  $\overline{CS}$  pin is low at any time. All others should be driven high.

**\*\*\***The device is stacked with 2-die, so it has a restriction in sequential operation: The address counter cannot cross the die boundary.

When the Address Pointer reaches the highest address of first die (3FFFFh), the address counter cannot cross to first address of 2nd die (40000h). Instead, it rolls over to (00000h). So the sequential operation must be terminated at the last address of first die (Die 0) by CS# HIGH, and begin new sequential operation from first address (40000h) of second die (Die 1) by CS# LOW.

| Γ | 1 | 2                                                         | 3                                                                                          | 4                                                                                                                                              | 5 6                              |

|---|---|-----------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4 |   |                                                           |                                                                                            |                                                                                                                                                | A                                |

| E | 3 | J1<br>Conn_01x06<br>MOSL_SI00<br>MISO_SI01<br>SCLK<br>GND | VDD<br>R1 U1<br>10K SPI_MEM<br>(MISO_SID1 + 0<br>S0/SI01 HOLD/SI03<br>4 VSS SI/SI00<br>GND | PWR_FLAG PWR_FLAG VDD                                                                                                                          | В                                |

|   |   |                                                           |                                                                                            |                                                                                                                                                | c                                |

| [ |   | 2                                                         | 3                                                                                          | Memory Solutions   Sheet: /   File: spi_ram_rev1.sch   Title: SPL_RAM_DUAL   Size: A4 Date: 2019-06-15   KiCad E.D.A. kicad 5.0.2-5.fc29   4 4 | D<br>Rev: Rev. 1<br>Id: 1/1<br>5 |